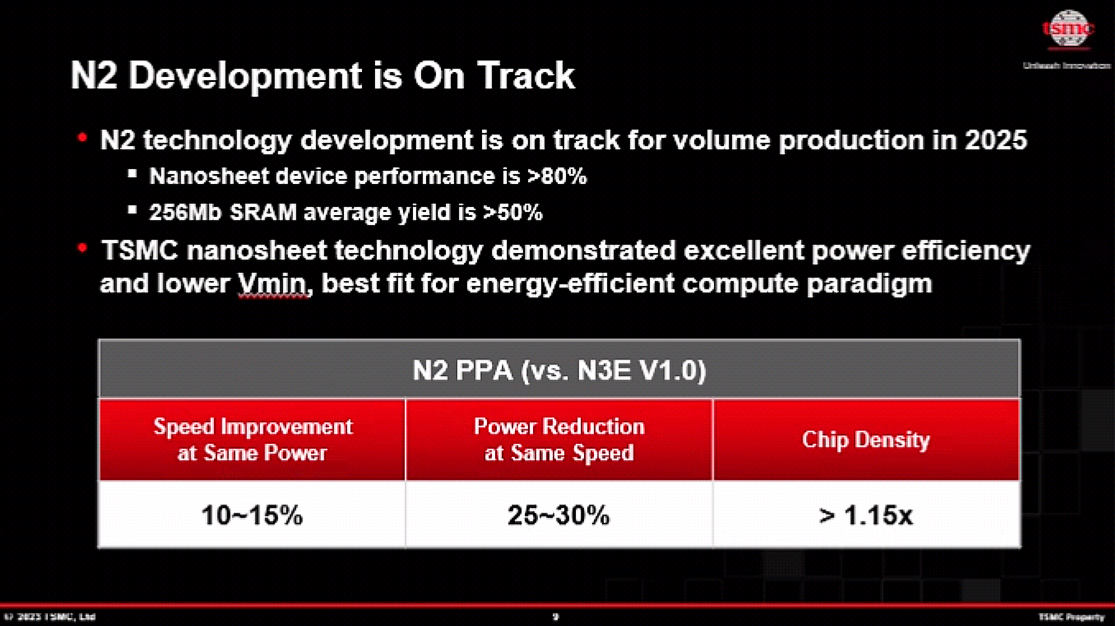

TSMC begins quietly volume production of 2nm-class chips — first GAA transistor for TSMC claims up to 15% improvement at ISO power

TSMC has quietly begun volume production of its 2nm-class N2 process in Q4 2025 as planned, marking the company’s first GAA nanosheet node that will be ramping production at two new fabs to meet strong demand from various customers.

(Image credit: TSMC)

TSMC has quietly revealed that it had commenced volume production of chips using its N2 (2nm-class) fabrication process. The company did not issue a formal press release notifying about the production start, but the firm had said multiple times that N2 was on track for volume manufacturing in Q4, so the plan has been fulfilled.

"TSMC’s 2nm (N2) technology has started volume production in 4Q25 as planned," a statement at TSMC's web page dedicated to 2nm Technology reads.

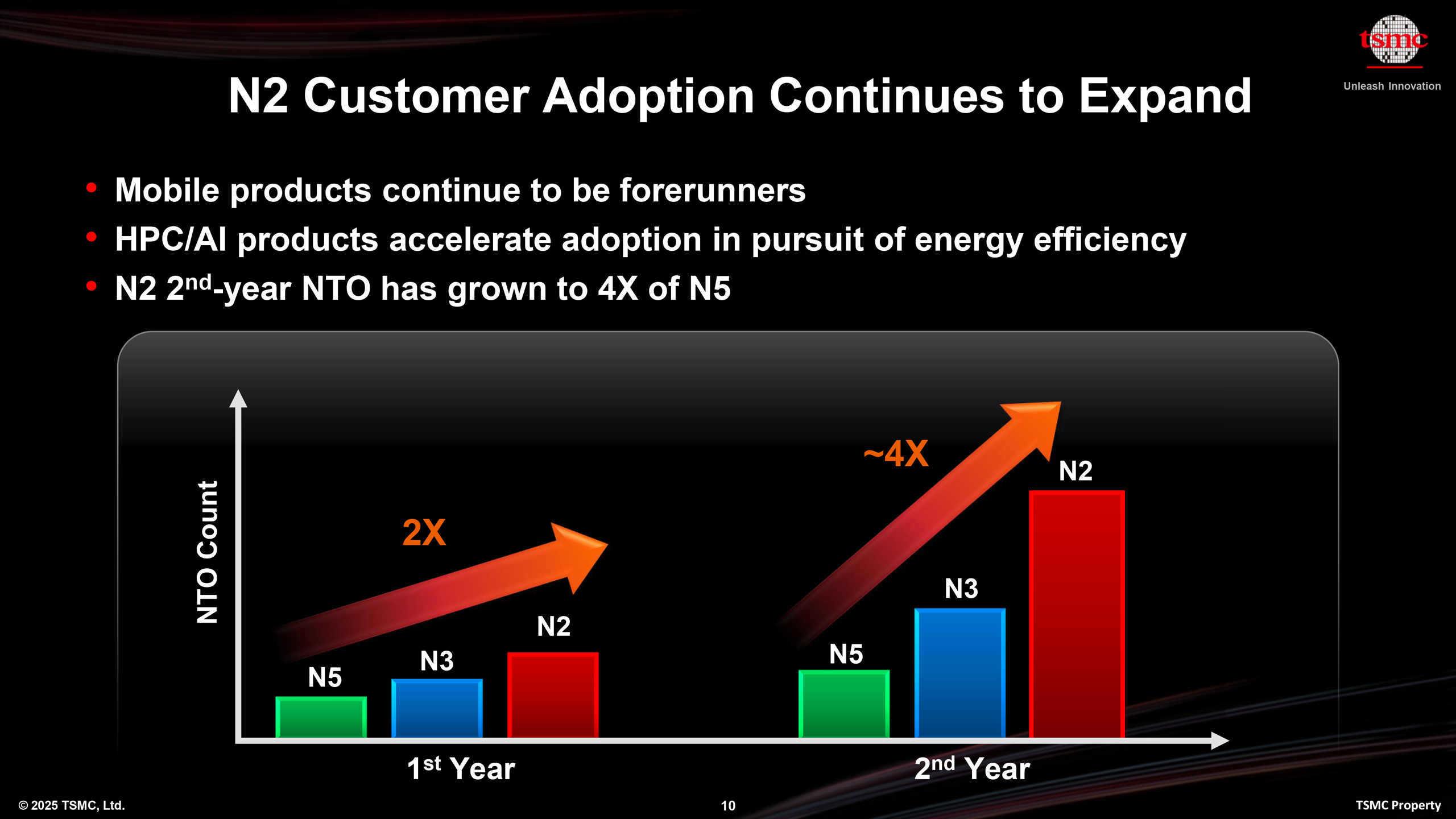

(Image credit: TSMC)

From an improvement standpoint, N2 is designed to deliver a 10%–15% performance gain at the same power, a 25%–30% reduction in power at the same performance, and a 15% increase in transistor density compared to N3E for mixed designs that include logic, analog, and SRAM. For logic-only designs, transistor density is up to 20% higher than N3E.

Swipe to scroll horizontally

Data announced during conference calls, events, press briefings and press releases. Compiled by Tom's Hardware

Row 0 - Cell 0

N2 vs N3E

N2P vs N3E

N2P vs N2

A16 vs N2P

N2X vs N2P

Power**

-25% ~ -30%

-36%

-5% ~ -10%

-15% ~ -20%

lower

Performance***

10% - 15%

18%

5% - 10%

8% - 10%

10%

Density*

1.15x

1.15x

?

1.07x - 1.10x

?

Transistor

GAA

GAA

GAA

GAA

GAA

Power Delivery

Front-side w/ SHPMIM

Front-side w/ SHPMIM

Front-side w/ SHPMIM

SPR

Front-side w/ SHPMIM (?)

HVM

H2 2025

H2 2026

H2 2026

H2 2026

2027

*Chip density published by TSMC reflects 'mixed' chip density consisting of 50% logic, 30% SRAM, and 20% analog. **At the same speed. ***At the same power.